The program can create a complete text representation of any group of objects by calling these strategies, which are virtually always already carried out in the base associative array class. For the literal illustration of an integer in Hexadecimal notation, prefix it by "0x" or "0X". This is the 4-bit parallel subtractor, nevertheless, we are able to implement a parallel subtractor by including any variety of full adders in the chain of the circuit shown in figure-2. It is clear that the logic circuit of a full adder consists of one XOR gate, three AND gates and one OR gate, that are related together as shown in Figure-2. Full adders are additionally used in technology of program counterpoints. Generally, flip-flops are used as the reminiscence element in sequential circuits. A latch is used to store 1 bit information in a digital system, so it is considered as probably the most elementary reminiscence component. In serial adder, the D flip-flop is used to store the carry output bit. A shift control is used to enable the shift registers A and B and the carry flip-flop.

The characteristic equations of the full adder, i.e. equations of sum (S) and carry output (Cout) are obtained in accordance with the principles of binary addition. Within the case of full subtractor, the 1s and 0s for the output variables (distinction and borrow) are decided from the subtraction of A - B - bin. But, we may notice a dedicate circuit to carry out the subtraction of two binary numbers. As we know that the half-subtractor can solely be used for subtraction of LSB (least important bit) of binary numbers. In this manner, the subtraction operation of binary numbers might be transformed into easy addition operation which makes hardware development simple and cheaper. This is how the binary adder-subtractor circuit performs both binary addition and binary subtraction operations. Thus, a full adder circuit adds three binary digits, the place two are the inputs and one is the carry forwarded from the previous addition.

The characteristic equations of the full adder, i.e. equations of sum (S) and carry output (Cout) are obtained in accordance with the principles of binary addition. Within the case of full subtractor, the 1s and 0s for the output variables (distinction and borrow) are decided from the subtraction of A - B - bin. But, we may notice a dedicate circuit to carry out the subtraction of two binary numbers. As we know that the half-subtractor can solely be used for subtraction of LSB (least important bit) of binary numbers. In this manner, the subtraction operation of binary numbers might be transformed into easy addition operation which makes hardware development simple and cheaper. This is how the binary adder-subtractor circuit performs both binary addition and binary subtraction operations. Thus, a full adder circuit adds three binary digits, the place two are the inputs and one is the carry forwarded from the previous addition.

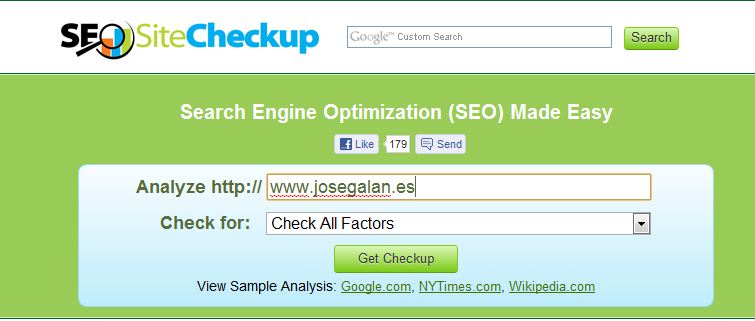

A combinational circuit which is designed to add three binary digits and produce two outputs is named full adder. The complete adder circuit provides three binary digits, srt to vtt where two are the inputs and one is the carry forwarded from the previous addition. It produces the sum bit S2 which is the second bit of the output sum, and a carry bit C2 can be produced which again forwarded to the following full adder FA3. It generates the sum bit S2 which is the second bit of the output sum, and the carry bit C2 that's connected to the following full adder FA3 within the chain. The circuit of the complete adder consists of two EX-OR gates, two AND gates and one OR gate, which are linked together as shown in the total adder circuit. Depending upon the variety of bits taken as enter, there are two sorts of subtractors specifically, Half Subtractor and Full Subtractor. Now that you’re acquainted with the several types of SEO Studio Tools, let’s discuss tips on how to profit from them in your optimization efforts.

On this chapter, let us talk about about the clock signal and forms of triggering one after the other. And a robust backlink profile can signal to serps that your moz website ranking is a trusted, authoritative useful resource. Half subtractor can also be used in amplifiers to compensate the sound distortion. Hence, for performing arithmetic operations at high velocity, we use half adder and full adder circuits. Full subtractors are also utilized in DSP (Digital Signal Processing) and networking based mostly methods. ADCs are essential parts in various knowledge acquisition programs used in the sphere of scientific research, industrial automation, and instrumentation. Redundancy: Implement redundant systems and fallback mechanisms for critical functions. A latch is an asynchronous sequential circuit whose output adjustments instantly with the change within the utilized enter. If the sequential circuit is operated with the clock sign when it's in Logic Low, then that kind of triggering is named Negative level triggering. Below these high level metrics, the next modules will likely be included in the Domain Authority Checker report. For example, the next domain authority score means that a site is more prone to rank effectively, making it an excellent backlink source. No knowledge discovered for this area and also you suspect it is because of us not being capable of finding hyperlink data for the area, you can head over to Link Explorer to double verify.